晶振基本資料及PCB布局設計指導

來源:http://m.11ed.cn 作者:金洛鑫電子 2019年08月20

我們都知道石英晶振大致可以分為兩大類,分別是MHz和KHz,一般來說MHz頻率范圍比KHz要高,而且范圍更廣泛,KHz的范圍雖然從32KHz~100KHz都有,但范圍小不說,市場上和用戶應用都是以32.768KHz這個頻點為主.因此使用KHz和MHz時,PCB板的布局和設計也會稍稍的不同,二者之間的參數,電氣特性,特征也會有一些差別.下面金洛鑫介紹一些晶振的基本資料,以及MHz和KHz的PCB板設計注意事項.

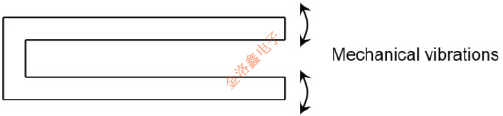

晶振利用振動壓電材料的機械諧振來產生非常穩定的時鐘信號.通常借助頻率提供穩定的時鐘信號或跟蹤時間;因此,晶振廣泛用于RF和數字電路.晶振可由不同供應商提供,形狀和尺寸也不盡相同,在性能和規格方面有很大差異.為在溫度、濕度、電源和工藝發生變化時使穩健的應用保持穩定,了解各個參數和貼片振蕩器電路至關重要.所有物理對象都具有固有的振動頻率,振動頻率由其形狀、大小、彈性和材料中的聲速決定.壓電材料在施加電場時會變形,在恢復到其原始形狀時會產生電場.電子電路中最常用的壓電材料是石英晶振,但也使用陶瓷諧振器—通常用于低成本或非時序關鍵型應用.32.768KHz晶振通常被切割成音叉形狀,可以形成非常精確的頻率.

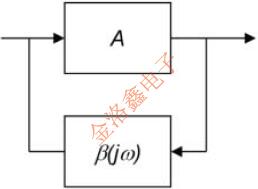

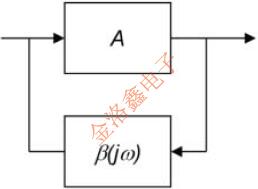

巴克豪森穩定性準則是用于確定電子電路何時振蕩的兩個條件.其中規定,如果A是電路中放大元件的增益,β(jω)是反饋路徑的傳遞函數,則電路將僅在符合以下條件的頻率下維持穩態振蕩:

環路增益的絕對值等于單位增益,即|βA|=1

環路的相移為0或2π的整數倍,即∠βA=2πn,n∈0、1、2、3...

第一條準則將確保恒定幅值信號.小于1的數會將信號衰減到0,大于1的數會將信號放大到無窮大.第二條準則將確保晶振穩定的頻率.對于其他相移值,正弦波輸出將因反饋環而被抵消.

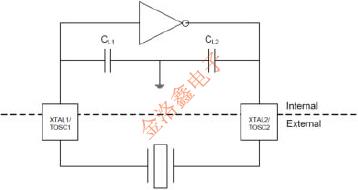

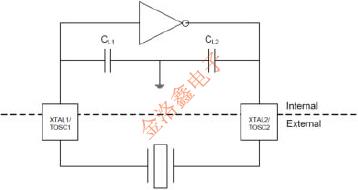

Microchip AVR單片機中的32.768kHz振蕩器如圖1-3所示,它由反相放大器(內部)和晶振(外部)組成.大多數AVR單片機都具有內部容性負載(CL1和CL2),因此通常不需要外部電容.但在某些情況下,必須添加外部負載以滿足晶振規范.某些AVR單片機可選擇應使用CKOPT熔絲連接還是斷開內部電容.反相放大器將提供一個π弧度(180度)相移,剩下的π弧度相移將由Quartz Crystal和容性負載(頻率為32.768KHz)提供,得到的總相移為2π弧度.在起振期間,放大器輸出將增大,直到建立環路增益為1的穩態振蕩,即滿足巴克豪森準則.此過程由AVR單片機振蕩器電路自動控制.

Microchip AVR單片機中的32.768kHz振蕩器如圖1-3所示,它由反相放大器(內部)和晶振(外部)組成.大多數AVR單片機都具有內部容性負載(CL1和CL2),因此通常不需要外部電容.但在某些情況下,必須添加外部負載以滿足晶振規范.某些AVR單片機可選擇應使用CKOPT熔絲連接還是斷開內部電容.反相放大器將提供一個π弧度(180度)相移,剩下的π弧度相移將由Quartz Crystal和容性負載(頻率為32.768KHz)提供,得到的總相移為2π弧度.在起振期間,放大器輸出將增大,直到建立環路增益為1的穩態振蕩,即滿足巴克豪森準則.此過程由AVR單片機振蕩器電路自動控制.

電氣模型

電氣模型

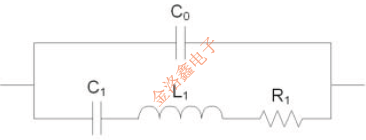

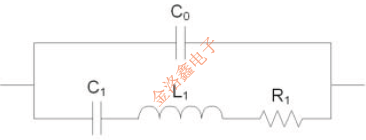

晶振的等效電路如圖1-4所示.串聯RLC網絡稱為動態臂,給出了晶振機械行為的電氣描述,其中C1表示石英的彈性,L1表示振動質量,R1表示由于阻尼造成的損失.C0稱為并聯電容或靜態電容,是晶振外殼和電極引起的電寄生電容的總和.如果使用電容表測量晶振電容,則只測量C0(C1無作用).

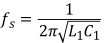

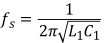

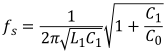

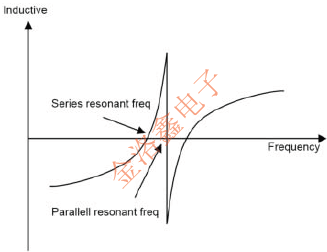

通過使用拉普拉斯變換,可以在該網絡中找到兩個諧振頻率.串聯諧振頻率fs僅取決于C1和L1,并聯或抗諧振頻率fp則還取決于C0.電抗與頻率特性如圖1-5所示.

通過使用拉普拉斯變換,可以在該網絡中找到兩個諧振頻率.串聯諧振頻率fs僅取決于C1和L1,并聯或抗諧振頻率fp則還取決于C0.電抗與頻率特性如圖1-5所示.

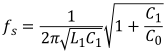

公式1-1.串聯諧振頻率

公式1-2.并聯諧振頻率

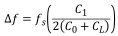

公式1-3.偏移的并聯諧振頻率

等效串聯電阻

等效串聯電阻(Equivalent Series Resistance,ESR)是機械損耗的電氣表示,在串聯諧振頻率fs下,它等于電氣模型中的R1.ESR是一個非常重要的參數,在晶振數據手冊中提供.ESR通常取決于晶振的物理尺寸,小晶振(特別是小型SMD晶振)的損耗和ESR值通常高于大晶振.ESR值越高,反相放大器的負載就越高,而ESR過高可能會導致振蕩器運行不穩定.無法實現單位增益,也無法滿足巴克豪森準則.

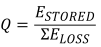

Q因數和穩定性

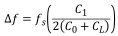

晶振的頻率穩定性通過Q因數來衡量.Q因數是存儲在晶振中的能量與所有能量損耗之和的比值.通常,石英晶振的Q值范圍為10,000至100,000,而LC振蕩器的Q值可能為100.陶瓷諧振器的Q值低于石英晶振,對容性負載更敏感(牽引能力更高).

公式1-4.Q因數

以下幾個因素會影響頻率穩定性:由安裝、沖擊或振動應力引起的機械應力、電源變化、負載阻抗變化、溫度變化、磁場變化、電場變化以及晶振老化都可能產生影響.晶振供應商通常會在其數據手冊中列出這些參數.

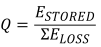

起振時間

在起振期間,噪聲將在反相放大器中放大.晶振將充當帶通濾波器并且僅反饋將被放大的晶振諧振頻率分量.在實現穩態振蕩之前,晶振/反相放大器環路的環路增益大于1,信號幅值將增大.達到穩態時,環路增益將滿足巴克豪森準則,環路增益為1,幅值恒定.

影響起振時間的因素:

•高ESR晶振的起振速度慢于低ESR晶振

高Q因數晶振的起振速度慢于低Q因數晶振

高負載電容會增加起振時間

振蕩器放大器驅動能力(有關振蕩器裕度的更多詳細信息,請參見第3.2節負電阻測試和安全系數).此外,晶振頻率也會影響起振時間(晶振頻率越高,起振就越快),但對于32.768kHz晶振,此參數固定.

溫度容差

溫度容差

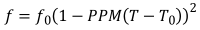

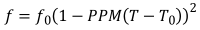

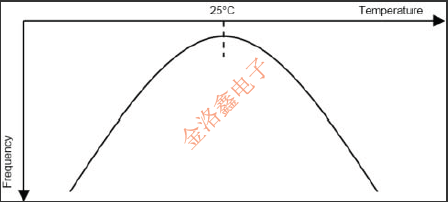

典型的32.768K通常被切割成使標稱頻率集中于25°C.高于和低于25°C時,頻率都將因拋物線特性而降低,如圖1-7所示.頻移由公式1-5得出,其中f0為T0時的目標頻率(25°C時通常為32.768KHz),PPM為晶振數據手冊提供的溫度容差系數.

公式1-5.溫度變化的影響

如果不謹慎考慮PCB布線和裝配過程中使用的材料,即使是性能最佳的振蕩器電路和高質量晶振也不會表現出良好性能.超低功耗32.768K石英振蕩子的功耗通常遠低于1μW,因此流入電路中的電流非常小.此外,晶振頻率高度依賴于容性負載.為提高振蕩器的穩健性,我們建議在PCB布線期間遵循以下準則:

•從XTAL1/TOSC1和XTAL2/TOSC2連接到晶振的信號線應盡可能短,以減小寄生電容并提高抗噪性和抗串擾性.應避免使用任何類型的插座.

•在晶振和信號線的周圍放置地平面和保護環,對其進行屏蔽.

•避免在晶振線附近布數字線(特別是時鐘線).對于多層PCB板,避免在晶振線下方布信號線.

•使用高質量PCB和焊接材料.

•灰塵和濕度會增加寄生電容并減弱信號隔離,因此建議使用保護涂層.

晶振利用振動壓電材料的機械諧振來產生非常穩定的時鐘信號.通常借助頻率提供穩定的時鐘信號或跟蹤時間;因此,晶振廣泛用于RF和數字電路.晶振可由不同供應商提供,形狀和尺寸也不盡相同,在性能和規格方面有很大差異.為在溫度、濕度、電源和工藝發生變化時使穩健的應用保持穩定,了解各個參數和貼片振蕩器電路至關重要.所有物理對象都具有固有的振動頻率,振動頻率由其形狀、大小、彈性和材料中的聲速決定.壓電材料在施加電場時會變形,在恢復到其原始形狀時會產生電場.電子電路中最常用的壓電材料是石英晶振,但也使用陶瓷諧振器—通常用于低成本或非時序關鍵型應用.32.768KHz晶振通常被切割成音叉形狀,可以形成非常精確的頻率.

圖1-1.32.768kHz音叉晶振的形狀

振蕩器巴克豪森穩定性準則是用于確定電子電路何時振蕩的兩個條件.其中規定,如果A是電路中放大元件的增益,β(jω)是反饋路徑的傳遞函數,則電路將僅在符合以下條件的頻率下維持穩態振蕩:

環路增益的絕對值等于單位增益,即|βA|=1

環路的相移為0或2π的整數倍,即∠βA=2πn,n∈0、1、2、3...

第一條準則將確保恒定幅值信號.小于1的數會將信號衰減到0,大于1的數會將信號放大到無窮大.第二條準則將確保晶振穩定的頻率.對于其他相移值,正弦波輸出將因反饋環而被抵消.

圖1-2.反饋環

圖1-3.AVR器件中的皮爾斯晶振電路(簡化電路)

晶振的等效電路如圖1-4所示.串聯RLC網絡稱為動態臂,給出了晶振機械行為的電氣描述,其中C1表示石英的彈性,L1表示振動質量,R1表示由于阻尼造成的損失.C0稱為并聯電容或靜態電容,是晶振外殼和電極引起的電寄生電容的總和.如果使用電容表測量晶振電容,則只測量C0(C1無作用).

圖1-4.晶振等效電路

公式1-1.串聯諧振頻率

公式1-2.并聯諧振頻率

圖1-5.晶振電抗特性

低于30MHz的晶振可工作在串聯和并聯諧振頻率之間的任何頻率下,即,其在工作時處于感性狀態.30MHz以上的高頻貼片晶振通常工作在串聯諧振頻率或泛音頻率下,泛音頻率出現在基頻的倍數處.向晶振添加容性負載CL將導致頻率偏移公式1-3中的值.晶振頻率可通過改變負載電容來調節,這稱為頻率牽引.公式1-3.偏移的并聯諧振頻率

等效串聯電阻

等效串聯電阻(Equivalent Series Resistance,ESR)是機械損耗的電氣表示,在串聯諧振頻率fs下,它等于電氣模型中的R1.ESR是一個非常重要的參數,在晶振數據手冊中提供.ESR通常取決于晶振的物理尺寸,小晶振(特別是小型SMD晶振)的損耗和ESR值通常高于大晶振.ESR值越高,反相放大器的負載就越高,而ESR過高可能會導致振蕩器運行不穩定.無法實現單位增益,也無法滿足巴克豪森準則.

Q因數和穩定性

晶振的頻率穩定性通過Q因數來衡量.Q因數是存儲在晶振中的能量與所有能量損耗之和的比值.通常,石英晶振的Q值范圍為10,000至100,000,而LC振蕩器的Q值可能為100.陶瓷諧振器的Q值低于石英晶振,對容性負載更敏感(牽引能力更高).

公式1-4.Q因數

以下幾個因素會影響頻率穩定性:由安裝、沖擊或振動應力引起的機械應力、電源變化、負載阻抗變化、溫度變化、磁場變化、電場變化以及晶振老化都可能產生影響.晶振供應商通常會在其數據手冊中列出這些參數.

起振時間

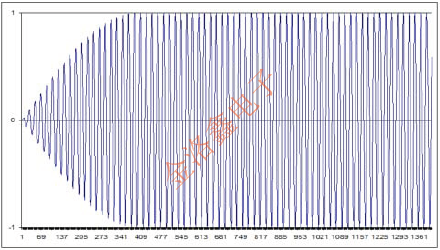

在起振期間,噪聲將在反相放大器中放大.晶振將充當帶通濾波器并且僅反饋將被放大的晶振諧振頻率分量.在實現穩態振蕩之前,晶振/反相放大器環路的環路增益大于1,信號幅值將增大.達到穩態時,環路增益將滿足巴克豪森準則,環路增益為1,幅值恒定.

影響起振時間的因素:

•高ESR晶振的起振速度慢于低ESR晶振

高Q因數晶振的起振速度慢于低Q因數晶振

高負載電容會增加起振時間

振蕩器放大器驅動能力(有關振蕩器裕度的更多詳細信息,請參見第3.2節負電阻測試和安全系數).此外,晶振頻率也會影響起振時間(晶振頻率越高,起振就越快),但對于32.768kHz晶振,此參數固定.

圖1-6.晶振的起振信號

典型的32.768K通常被切割成使標稱頻率集中于25°C.高于和低于25°C時,頻率都將因拋物線特性而降低,如圖1-7所示.頻移由公式1-5得出,其中f0為T0時的目標頻率(25°C時通常為32.768KHz),PPM為晶振數據手冊提供的溫度容差系數.

公式1-5.溫度變化的影響

圖1-7.典型溫度與晶振頻率特性

PCB布線和設計注意事項布線和設計注意事項如果不謹慎考慮PCB布線和裝配過程中使用的材料,即使是性能最佳的振蕩器電路和高質量晶振也不會表現出良好性能.超低功耗32.768K石英振蕩子的功耗通常遠低于1μW,因此流入電路中的電流非常小.此外,晶振頻率高度依賴于容性負載.為提高振蕩器的穩健性,我們建議在PCB布線期間遵循以下準則:

•從XTAL1/TOSC1和XTAL2/TOSC2連接到晶振的信號線應盡可能短,以減小寄生電容并提高抗噪性和抗串擾性.應避免使用任何類型的插座.

•在晶振和信號線的周圍放置地平面和保護環,對其進行屏蔽.

•避免在晶振線附近布數字線(特別是時鐘線).對于多層PCB板,避免在晶振線下方布信號線.

•使用高質量PCB和焊接材料.

•灰塵和濕度會增加寄生電容并減弱信號隔離,因此建議使用保護涂層.

正在載入評論數據...

發表評論:

| 姓名: | |

| 郵箱: | |

| 正文: | |

歡迎參與討論,請在這里發表您的看法、交流您的觀點。

相關資訊

- [2023-06-29]-40~+105°C時的6G貼片石英晶體...

- [2020-07-16]通信網絡時鐘系統7x5mm溫補晶振...

- [2020-07-06]時鐘網絡與OCXO振蕩器的階層級別...

- [2020-06-22]Jauch公司專門為導航開發的新TC...

- [2020-06-06]解鎖Statek振蕩器系列產品的品質...

- [2020-05-28]VV-800系列VCXO晶體振蕩器的包裝...

- [2020-04-30]獨家推薦MEMS振蕩器應用電機系統...

- [2020-04-25]海外各大元件供應商紛紛停工,是...

業務經理

業務經理 客服經理

客服經理