Silicon頻率靈活的晶體振蕩器原型設計

來源:http://m.11ed.cn 作者:金洛鑫電子 2019年07月20

每一款晶體振蕩器系列料號,都是有固定的頻率范圍的,根據范圍的大小可以分為高頻和低頻,但是這樣也失去了靈活性的優勢.例如一顆低頻的石英晶體振蕩器性能和特性特別適合用于產品身上,但是頻率范圍達不到要求,這會使設計者和采購感到困擾,因此,美國一個叫做Silicon晶振的品牌,專門開發設計了具有頻率靈活性的振蕩器系列,本文將揭示其制造的設計原型及工作原理.

具有頻率柔性晶體振蕩器的原型制作:

理想情況下,新系統的開發人員應該在設計過程的早期就做出時鐘要求的決定.雖然時鐘頻率是應該預先知道的關鍵參數,但確定這些頻率有時需要實驗和重新評估.在設計的原型和驗證階段快速改變時鐘頻率的能力可以加快上市時間.使用頻率靈活的可編程晶體振蕩器(XOs)作為原型工具,可以簡化驗證系統性能的過程,并有助于簡化整個產品開發周期.

評估多個頻率:

當進行任何系統設計工作時,頻率變化通常在設計周期的后期變得必要.例如,在開發過程中嘗試和優化時鐘速率通常會提高性能和設計效率.在其他情況下,設計中的錯誤或誤判可能需要改變頻率.在任何一種情況下,使用能夠適應最后時刻變化的XO都是有幫助的,而不必改變材料清單或印刷電路板布局,特別是因為固定頻率OSC晶振的交付周期可能會延長幾周甚至幾個月.

最后一刻的改變非常普遍,尤其是在基于現場可編程門陣列的應用中.FPGAs的極大靈活性意味著可以快速調整邏輯路徑寬度和數據速率,以提高功率、吞吐量或門利用率.例如,在FPGA設計的最后階段,改變數據路徑寬度或降低時鐘速率可能是關閉時序的有效方法.此外,可能會有混合信號電路,如片內串行器/解串行器(SerDes)收發器,它們可能會受益于時鐘優化.輸出抖動性能和誤碼率通常直接取決于基準時鐘頻率.快速改變時鐘頻率的能力有助于達到最佳時鐘速率.

頻率余量微調:

在生產測試期間,使用標準頻率的系統也可以從頻率靈活的有源晶振中獲益,用于設計驗證和頻率余量調整.雖然以太網媒體訪問控制或PHY可以指定156.25兆赫的參考XO,但固定頻率的參考不能實現速率容差.為了給系統留出余量,設計人員必須使用能夠產生156.25+100ppm和156.25-100ppmMHz的外部時鐘源,或者他們必須返工電路板以安裝更快或更慢的XOs.這種方法變得有限且耗時,尤其是在多種溫度條件下測試多個電路板時.

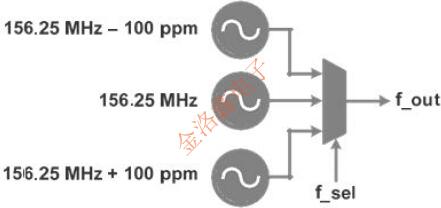

頻率余量微調也可以使用多個XO和一個多路復用器來實現,如圖1所示.這種方案的缺點包括頻率數量有限以及在頻率之間切換時會引入額外的噪聲和相位不連續性.這種方法還需要不同的印刷電路板尺寸來進行驗證和生產. 使用外部時鐘源或多個XO來執行頻率裕度調節通常會限制設計人員進行精細頻率調整或驗證連續頻率以排除可疑問題區域的能力.由于獲得額外時鐘頻率所需的前置時間,此問題可能導致增加的返工和延遲增加.例如,如果系統工作在+100ppm但在+55ppm處失敗,則這些方法都不能有效地捕獲該故障.

傳統的頻率靈活XO不能應對挑戰:

解決頻率裕度問題的一個更好的方法是使用在線可編程XO,它可以產生具有非常高的增量頻率分辨率的連續頻率,而不會引入相位毛刺或損害相位抖動性能.傳統的XO晶振無法實現這種頻率靈活性,因為它們依賴于機械調諧的石英晶體,這些石英晶體被切割以在特定頻率下諧振.每個新頻率需要不同的晶體尺寸.

為滿足這一需求,傳統的XO供應商使用模擬電路技術,如鎖相環(PLL)來克服傳統晶體振蕩器的頻率剛性.但是,模擬PLL通常限于二次冪或整數倍頻.這些解決方案無法滿足為設計人員提供全頻率編程或“調整”靈活性所需的頻率分辨率.

電源抑制性能也影響系統原型和調試時間模擬PLL對噪聲非常敏感,通常通過電源和內部VCO將噪聲源耦合和放大到輸出時鐘信號.這種靈敏度可以防止模擬PLL在高性能系統中驅動超低抖動時鐘信號,在這些系統中,時鐘靈活性很重要且環境容易產生噪聲和惡意.為了解決所有這些電源噪聲,必須經常在時間關鍵的原型調試階段修改或重新設計PCB,這會顯著延遲系統驗證和最終的生產發布.

系統噪聲主要是由于瞬態負載切換電流以及大多數計算機,通信和消費系統中開關模式電源(SMPS)的廣泛使用.為了對抗這些SMPS產生的噪聲和紋波,集成的片上電源電壓調節和濾波不僅成為固定SPXO振蕩器的必要功能,也成為可編程XO的必要功能.集成調節和濾波有助于抑制電源軌上常見的噪聲,從而不會影響輸出時鐘的抖動性能.在大多數情況下,與傳統的基于模擬的XO相比,額外的PSR性能將改善抖動容限,擴展鏈路范圍并增強系統性能.

集成濾波和調節可直接轉化為材料清單成本和元件數量的節省,因為設計人員可以最小化甚至消除外部電源濾波器和鐵氧體磁珠元件,以保持足夠的抖動性能.例如,假設基于模擬鎖相環的XO的電源上存在100千伏安范圍為100千赫至1兆赫的正弦紋波.提高系統功率效率所需的開關電源通常在此頻率范圍內工作.電源上如此大的噪聲會降低典型XOs的抖動性能,使用基于模擬的鎖相環,無需片內濾波和調節,從約10ps(無電源噪聲)降至50ps(有電源噪聲).抖動性能的降低使得基于模擬鎖相環的普通異或不適合高速網絡應用,如千兆以太網和萬兆以太網.

底線是什么?基于模擬鎖相環的XOs的性能和頻率限制迫使系統設計者使用通常缺乏集成電源調節和濾波的固定頻率器件.結果,設計師們發現自己回到了起點,沒有多少選擇.

I2C數字可編程XOs提供多功能解決方案:

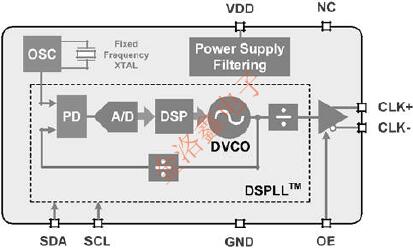

I2C數字可編程XOs為固定頻率XOs提供了靈活的替代方案.例如,如圖2所示,硅實驗室的可編程振蕩器結合了傳統的固定頻率晶體基準電壓源和專利數字鎖相環技術,以提供頻率分辨率優于每萬億分之26的I2C可編程輸出.由于其獨特的數字電路和廣泛的內部電源調節濾波,基于數字鎖相環技術的OSC振蕩器可以輕松實現與基于固定頻率聲表面波振蕩器相當的抖動性能.I2C可編程振蕩器能夠在不犧牲性能的情況下評估系統中的任何頻率.此外,I2C可編程XO可以用默認啟動頻率訂購,它們與固定頻率XO引腳和性能兼容. 通過使用頻率靈活、I2C可編程晶振作為原型工具,開發人員可以大大簡化驗證和最大化系統性能的過程,同時簡化整個產品開發周期.能夠在不改變材料清單、返工電路板設計或等待長交付周期XOs的情況下改變時鐘頻率,有助于設計師在優化特性和性能的同時實現業務關鍵型上市時間目標.

具有頻率柔性晶體振蕩器的原型制作:

理想情況下,新系統的開發人員應該在設計過程的早期就做出時鐘要求的決定.雖然時鐘頻率是應該預先知道的關鍵參數,但確定這些頻率有時需要實驗和重新評估.在設計的原型和驗證階段快速改變時鐘頻率的能力可以加快上市時間.使用頻率靈活的可編程晶體振蕩器(XOs)作為原型工具,可以簡化驗證系統性能的過程,并有助于簡化整個產品開發周期.

評估多個頻率:

當進行任何系統設計工作時,頻率變化通常在設計周期的后期變得必要.例如,在開發過程中嘗試和優化時鐘速率通常會提高性能和設計效率.在其他情況下,設計中的錯誤或誤判可能需要改變頻率.在任何一種情況下,使用能夠適應最后時刻變化的XO都是有幫助的,而不必改變材料清單或印刷電路板布局,特別是因為固定頻率OSC晶振的交付周期可能會延長幾周甚至幾個月.

最后一刻的改變非常普遍,尤其是在基于現場可編程門陣列的應用中.FPGAs的極大靈活性意味著可以快速調整邏輯路徑寬度和數據速率,以提高功率、吞吐量或門利用率.例如,在FPGA設計的最后階段,改變數據路徑寬度或降低時鐘速率可能是關閉時序的有效方法.此外,可能會有混合信號電路,如片內串行器/解串行器(SerDes)收發器,它們可能會受益于時鐘優化.輸出抖動性能和誤碼率通常直接取決于基準時鐘頻率.快速改變時鐘頻率的能力有助于達到最佳時鐘速率.

頻率余量微調:

在生產測試期間,使用標準頻率的系統也可以從頻率靈活的有源晶振中獲益,用于設計驗證和頻率余量調整.雖然以太網媒體訪問控制或PHY可以指定156.25兆赫的參考XO,但固定頻率的參考不能實現速率容差.為了給系統留出余量,設計人員必須使用能夠產生156.25+100ppm和156.25-100ppmMHz的外部時鐘源,或者他們必須返工電路板以安裝更快或更慢的XOs.這種方法變得有限且耗時,尤其是在多種溫度條件下測試多個電路板時.

頻率余量微調也可以使用多個XO和一個多路復用器來實現,如圖1所示.這種方案的缺點包括頻率數量有限以及在頻率之間切換時會引入額外的噪聲和相位不連續性.這種方法還需要不同的印刷電路板尺寸來進行驗證和生產. 使用外部時鐘源或多個XO來執行頻率裕度調節通常會限制設計人員進行精細頻率調整或驗證連續頻率以排除可疑問題區域的能力.由于獲得額外時鐘頻率所需的前置時間,此問題可能導致增加的返工和延遲增加.例如,如果系統工作在+100ppm但在+55ppm處失敗,則這些方法都不能有效地捕獲該故障.

傳統的頻率靈活XO不能應對挑戰:

解決頻率裕度問題的一個更好的方法是使用在線可編程XO,它可以產生具有非常高的增量頻率分辨率的連續頻率,而不會引入相位毛刺或損害相位抖動性能.傳統的XO晶振無法實現這種頻率靈活性,因為它們依賴于機械調諧的石英晶體,這些石英晶體被切割以在特定頻率下諧振.每個新頻率需要不同的晶體尺寸.

為滿足這一需求,傳統的XO供應商使用模擬電路技術,如鎖相環(PLL)來克服傳統晶體振蕩器的頻率剛性.但是,模擬PLL通常限于二次冪或整數倍頻.這些解決方案無法滿足為設計人員提供全頻率編程或“調整”靈活性所需的頻率分辨率.

電源抑制性能也影響系統原型和調試時間模擬PLL對噪聲非常敏感,通常通過電源和內部VCO將噪聲源耦合和放大到輸出時鐘信號.這種靈敏度可以防止模擬PLL在高性能系統中驅動超低抖動時鐘信號,在這些系統中,時鐘靈活性很重要且環境容易產生噪聲和惡意.為了解決所有這些電源噪聲,必須經常在時間關鍵的原型調試階段修改或重新設計PCB,這會顯著延遲系統驗證和最終的生產發布.

系統噪聲主要是由于瞬態負載切換電流以及大多數計算機,通信和消費系統中開關模式電源(SMPS)的廣泛使用.為了對抗這些SMPS產生的噪聲和紋波,集成的片上電源電壓調節和濾波不僅成為固定SPXO振蕩器的必要功能,也成為可編程XO的必要功能.集成調節和濾波有助于抑制電源軌上常見的噪聲,從而不會影響輸出時鐘的抖動性能.在大多數情況下,與傳統的基于模擬的XO相比,額外的PSR性能將改善抖動容限,擴展鏈路范圍并增強系統性能.

集成濾波和調節可直接轉化為材料清單成本和元件數量的節省,因為設計人員可以最小化甚至消除外部電源濾波器和鐵氧體磁珠元件,以保持足夠的抖動性能.例如,假設基于模擬鎖相環的XO的電源上存在100千伏安范圍為100千赫至1兆赫的正弦紋波.提高系統功率效率所需的開關電源通常在此頻率范圍內工作.電源上如此大的噪聲會降低典型XOs的抖動性能,使用基于模擬的鎖相環,無需片內濾波和調節,從約10ps(無電源噪聲)降至50ps(有電源噪聲).抖動性能的降低使得基于模擬鎖相環的普通異或不適合高速網絡應用,如千兆以太網和萬兆以太網.

底線是什么?基于模擬鎖相環的XOs的性能和頻率限制迫使系統設計者使用通常缺乏集成電源調節和濾波的固定頻率器件.結果,設計師們發現自己回到了起點,沒有多少選擇.

I2C數字可編程XOs提供多功能解決方案:

I2C數字可編程XOs為固定頻率XOs提供了靈活的替代方案.例如,如圖2所示,硅實驗室的可編程振蕩器結合了傳統的固定頻率晶體基準電壓源和專利數字鎖相環技術,以提供頻率分辨率優于每萬億分之26的I2C可編程輸出.由于其獨特的數字電路和廣泛的內部電源調節濾波,基于數字鎖相環技術的OSC振蕩器可以輕松實現與基于固定頻率聲表面波振蕩器相當的抖動性能.I2C可編程振蕩器能夠在不犧牲性能的情況下評估系統中的任何頻率.此外,I2C可編程XO可以用默認啟動頻率訂購,它們與固定頻率XO引腳和性能兼容. 通過使用頻率靈活、I2C可編程晶振作為原型工具,開發人員可以大大簡化驗證和最大化系統性能的過程,同時簡化整個產品開發周期.能夠在不改變材料清單、返工電路板設計或等待長交付周期XOs的情況下改變時鐘頻率,有助于設計師在優化特性和性能的同時實現業務關鍵型上市時間目標.

正在載入評論數據...

相關資訊

- [2024-03-08]IQD晶體尺寸縮小的設計效果LFXT...

- [2024-03-07]Golledge衛星通信中的頻率控制產...

- [2024-03-07]Golledge工業自動化和控制系統中...

- [2024-03-06]MTI-milliren恒溫晶振222系列振...

- [2024-03-06]MTI-milliren低G靈敏度銫原子鐘...

- [2024-03-05]GEYER高穩定性KXO-V93T低功耗32...

- [2024-03-02]NEL為系統關鍵應用程序設計和制...

- [2024-01-06]溫補補償振蕩器的原理及特點

業務經理

業務經理 客服經理

客服經理