Pletronics差分晶振PECL時鐘和終端

來源:http://m.11ed.cn 作者:金洛鑫電子 2019年02月18

晶振的發展與人類的生活是息息相關的,從上世紀40年代開始,石英晶體就作為主要的電子元器件黑線在我們身邊,在這幾十年中,頻率元件行業得到重大突破,無論是工藝還是技術,都達到非常高的標準,從KHZ,MHZ到GHZ,無不驗證晶振的成長。現在國內外各大晶振廠家和工程師,都在研發LVDS,LV-PECL差分晶振,因為它對于現在的科技發展有著比較大的作用。LV-PECL,LCMOS,LVDS,ECL都是差分晶體振蕩器的輸出方式,從ECL開始。

ECL的歷史:

ECL于1962年由摩托羅拉首次以IC形式引入,作為其單片發射極耦合邏輯(MECL1)。它是最古老的IC邏輯形式之一。這種形式的邏輯導致比DTL或TTL更快的運行速度并且還很好地融入了IC流程:

它取決于電阻比,而不是絕對值;所有匹配的晶體管使設計更容易;晶體管工作在線性區域或關閉,從不處于飽和模式,這增加了處理步驟;讓晶體管快速恢復。

許多組件適合一個隔離區域,這導致有效的芯片尺寸。與其他解決方案相比,功耗非常高。所有設備的輸出都設計為終止,信號擺動很小。這些要點賦予ECL獨特的特征。該ECL邏輯不斷發展,現在可用于GHz范圍。這是永遠的縮小石英晶振尺寸,采用RFSiGe工藝實現低噪聲和最佳速度。

ECL如何連接系統:

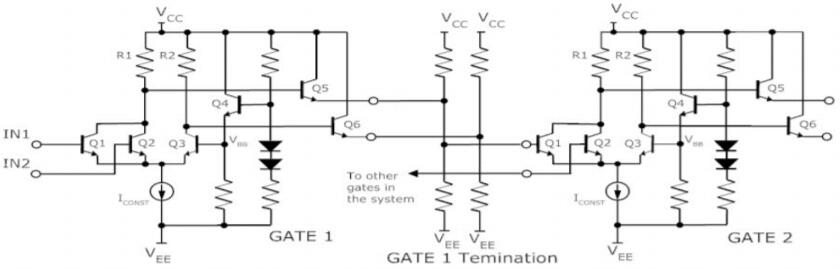

上述邏輯門可以連接到其他門以開始執行系統功能。 為了獲得最佳性能,必須終止兩個輸出。如果只使用一個輸出,則為占空比和抖動可能會受到不利影響。在此示例中,終止GATE1輸出,然后一個信號連接到另一個信號的GATE2,GATE2輸入可以來自系統中的某些其他ECL信號。由于邏輯電平以正引線為參考且邏輯電平較小,因此為正功率電源分配對于獲得最佳抗噪聲和抖動性能至關重要。

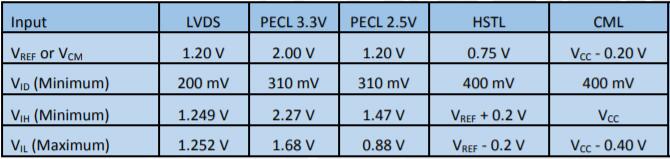

LVDS和PECL輸入電平:

ECL邏輯如何工作:

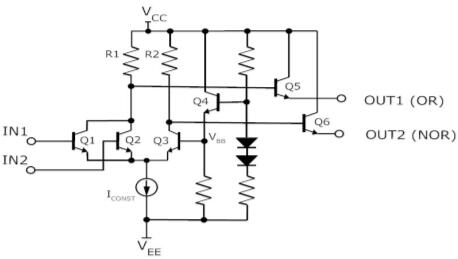

基本門如下所示:

ECL邏輯如何工作:

基本門如下所示:

如果IN1和IN2均低于VBB,則:

•ICONST的所有電流都將通過Q3。實際上IN1和IN2只需要低于120mV用于R2中電流的VBB是R1中的電流的100倍。

•R1上的壓降僅為Q5的基極電流。邏輯高(VHI)則約為一個VBE(1二極管壓降)低于正電源。

•能夠連接到更多邏輯門而沒有晶體管處于飽和狀態(集電極電壓遠低于基極電壓)的目標,邏輯電平或擺幅需要大約為一個VBE。因此,邏輯低(VLO)約為兩個VBE量。如果IN1和IN2中的任何一個或兩個都高于VBB,那么:

•ICONST的所有電流都將通過Q1或Q2。實際上IN1和IN2只需要約120mV在VBB之上,R1中的電流是R2的100倍。

•R2兩端的電壓降僅為Q6的基極電流。邏輯高(VHI)則約為一個VBE(1二極管壓降)低于正電源。

•R1上的壓降約為一個VBE,因此OUT2將比正電源低約兩個VBE壓降。ECL型輸出是晶體管的發射極。沒有下拉,因此下拉必須是外部。這樣做有幾個原因:

•此邏輯旨在實現非常高的速度,因此需要終止線路以控制振鈴和來自傳輸線的反射結束。發射極跟隨器提供低阻抗輸出終端。

•端接通常在25歐姆至100歐姆范圍內。這將導致IC中的功率過大如果在內部完成。

•對于比正電源節點低2.0伏的節點,終端通常為50歐姆。

•執行邏輯門時,輸出可以連接在一起。這形成了另一個稱為“線或”的邏輯點這不會增加任何增加的門延遲。

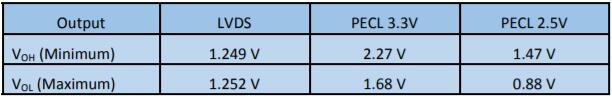

差分晶振LVDS和PECL輸出電平:

LVDS電平不隨電源電壓而變化,PECL輸出電平遵循電源電壓,顯示的值僅適用于標稱電源電壓。

Pletronics Crystal公司PECLVCXO系列源自PE9器件,因此具有相同的特性作為PE9系列。

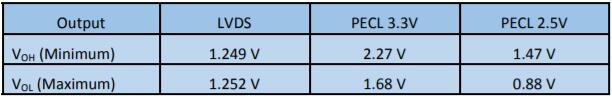

LVDS電平不隨電源電壓而變化,PECL輸出電平遵循電源電壓,顯示的值僅適用于標稱電源電壓。

Pletronics Crystal公司PECLVCXO系列源自PE9器件,因此具有相同的特性作為PE9系列。

ECL,PECL和LV-PECL的區別是什么?

ECL,PECL或LV-PECL晶振之間沒有區別。對于這種類型的電路,負引線中的電流幾乎是恒定的,沒有開關瞬變。該差分級用恒定電流源偏置。VBB推導支路是電阻性的而不是隨輸入水平而變化。正電源引線具有輸出瞬態,可為任何不匹配的容性負載充電。

選擇ECL從地面到負面供應。因此,具有最大瞬態的器件引線連接到地平面。這導致了以地面和地面為參考的邏輯電平變得有點獨立于電源電壓。

由于許多系統采用5.0V的TTL或CMOS邏輯工作,設計人員開始使用ECL,正極引線連接到+5.0V,負極引線接地。這增加了一些設計和布局需求但這也意味著系統中只需要少一個電源。因此,如果差分晶體振蕩器ECL是積極的,那么ECL是正ECL或PECL。值得注意的是,這是一個術語變化,但所涉及的IC不需要改變。

隨著時間的推移,系統電源電壓降低,通常降至3.3V和2.5V,以及術語低電壓正發射極耦合邏輯(LVPECL)被創造出來。

總結一下,ECL,PECL和LVPECL的原理圖可以相同,電阻值可能會發生變化較低的電壓。這些術語比基于技術的變化更基于市場營銷。

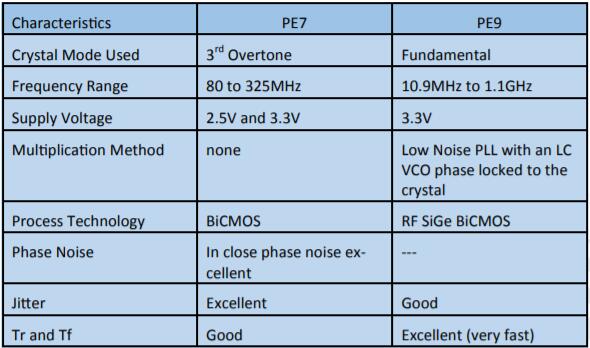

Pletronics Crystal的PE7和PE9系列時鐘振蕩器的區別是什么?時鐘振蕩器?

Pletronics提供各種PECL輸出解決方案。這些解決方案都符合通常所接受的PECL晶振規范。這些在實現輸出頻率的方法上不同。

一般來說時鐘信號就是差分信號,可以最大限度的減少電磁干擾和射頻干擾,而且頻率范圍可以從1.000MHZ~1000.000MHZ之間選擇,輸出的終端信號擁有低阻抗性。LV-PECL和PECL其實是一樣的,只是帶LV表示是低電源電壓的,差分信號輸出的石英晶體振蕩器電壓范圍最大不超過+5.0V,最低的才+1.8V,早已實現低電壓,低電流,因此許多人認為沒必要再加LV了。

ECL的歷史:

ECL于1962年由摩托羅拉首次以IC形式引入,作為其單片發射極耦合邏輯(MECL1)。它是最古老的IC邏輯形式之一。這種形式的邏輯導致比DTL或TTL更快的運行速度并且還很好地融入了IC流程:

它取決于電阻比,而不是絕對值;所有匹配的晶體管使設計更容易;晶體管工作在線性區域或關閉,從不處于飽和模式,這增加了處理步驟;讓晶體管快速恢復。

許多組件適合一個隔離區域,這導致有效的芯片尺寸。與其他解決方案相比,功耗非常高。所有設備的輸出都設計為終止,信號擺動很小。這些要點賦予ECL獨特的特征。該ECL邏輯不斷發展,現在可用于GHz范圍。這是永遠的縮小石英晶振尺寸,采用RFSiGe工藝實現低噪聲和最佳速度。

ECL如何連接系統:

上述邏輯門可以連接到其他門以開始執行系統功能。 為了獲得最佳性能,必須終止兩個輸出。如果只使用一個輸出,則為占空比和抖動可能會受到不利影響。在此示例中,終止GATE1輸出,然后一個信號連接到另一個信號的GATE2,GATE2輸入可以來自系統中的某些其他ECL信號。由于邏輯電平以正引線為參考且邏輯電平較小,因此為正功率電源分配對于獲得最佳抗噪聲和抖動性能至關重要。

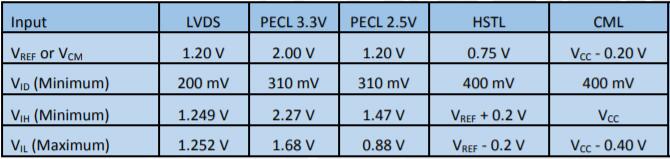

LVDS和PECL輸入電平:

如果IN1和IN2均低于VBB,則:

•ICONST的所有電流都將通過Q3。實際上IN1和IN2只需要低于120mV用于R2中電流的VBB是R1中的電流的100倍。

•R1上的壓降僅為Q5的基極電流。邏輯高(VHI)則約為一個VBE(1二極管壓降)低于正電源。

•能夠連接到更多邏輯門而沒有晶體管處于飽和狀態(集電極電壓遠低于基極電壓)的目標,邏輯電平或擺幅需要大約為一個VBE。因此,邏輯低(VLO)約為兩個VBE量。如果IN1和IN2中的任何一個或兩個都高于VBB,那么:

•ICONST的所有電流都將通過Q1或Q2。實際上IN1和IN2只需要約120mV在VBB之上,R1中的電流是R2的100倍。

•R2兩端的電壓降僅為Q6的基極電流。邏輯高(VHI)則約為一個VBE(1二極管壓降)低于正電源。

•R1上的壓降約為一個VBE,因此OUT2將比正電源低約兩個VBE壓降。ECL型輸出是晶體管的發射極。沒有下拉,因此下拉必須是外部。這樣做有幾個原因:

•此邏輯旨在實現非常高的速度,因此需要終止線路以控制振鈴和來自傳輸線的反射結束。發射極跟隨器提供低阻抗輸出終端。

•端接通常在25歐姆至100歐姆范圍內。這將導致IC中的功率過大如果在內部完成。

•對于比正電源節點低2.0伏的節點,終端通常為50歐姆。

•執行邏輯門時,輸出可以連接在一起。這形成了另一個稱為“線或”的邏輯點這不會增加任何增加的門延遲。

差分晶振LVDS和PECL輸出電平:

ECL,PECL和LV-PECL的區別是什么?

ECL,PECL或LV-PECL晶振之間沒有區別。對于這種類型的電路,負引線中的電流幾乎是恒定的,沒有開關瞬變。該差分級用恒定電流源偏置。VBB推導支路是電阻性的而不是隨輸入水平而變化。正電源引線具有輸出瞬態,可為任何不匹配的容性負載充電。

選擇ECL從地面到負面供應。因此,具有最大瞬態的器件引線連接到地平面。這導致了以地面和地面為參考的邏輯電平變得有點獨立于電源電壓。

由于許多系統采用5.0V的TTL或CMOS邏輯工作,設計人員開始使用ECL,正極引線連接到+5.0V,負極引線接地。這增加了一些設計和布局需求但這也意味著系統中只需要少一個電源。因此,如果差分晶體振蕩器ECL是積極的,那么ECL是正ECL或PECL。值得注意的是,這是一個術語變化,但所涉及的IC不需要改變。

隨著時間的推移,系統電源電壓降低,通常降至3.3V和2.5V,以及術語低電壓正發射極耦合邏輯(LVPECL)被創造出來。

總結一下,ECL,PECL和LVPECL的原理圖可以相同,電阻值可能會發生變化較低的電壓。這些術語比基于技術的變化更基于市場營銷。

Pletronics Crystal的PE7和PE9系列時鐘振蕩器的區別是什么?時鐘振蕩器?

Pletronics提供各種PECL輸出解決方案。這些解決方案都符合通常所接受的PECL晶振規范。這些在實現輸出頻率的方法上不同。

一般來說時鐘信號就是差分信號,可以最大限度的減少電磁干擾和射頻干擾,而且頻率范圍可以從1.000MHZ~1000.000MHZ之間選擇,輸出的終端信號擁有低阻抗性。LV-PECL和PECL其實是一樣的,只是帶LV表示是低電源電壓的,差分信號輸出的石英晶體振蕩器電壓范圍最大不超過+5.0V,最低的才+1.8V,早已實現低電壓,低電流,因此許多人認為沒必要再加LV了。

正在載入評論數據...

相關資訊

- [2024-03-08]IQD晶體尺寸縮小的設計效果LFXT...

- [2024-03-07]Golledge衛星通信中的頻率控制產...

- [2024-03-07]Golledge工業自動化和控制系統中...

- [2024-03-06]MTI-milliren恒溫晶振222系列振...

- [2024-03-06]MTI-milliren低G靈敏度銫原子鐘...

- [2024-03-05]GEYER高穩定性KXO-V93T低功耗32...

- [2024-03-02]NEL為系統關鍵應用程序設計和制...

- [2024-01-06]溫補補償振蕩器的原理及特點

業務經理

業務經理 客服經理

客服經理