異步時鐘與同步時鐘的晶體振蕩器使用解決方案

來源:http://m.11ed.cn 作者:金洛鑫電子 2019年09月18

時鐘源是每種產品內部都比較重要的模塊,決定了產品使用的壽命,性能,功能以及精準性,可以分為同步時鐘和異步時鐘.因為要求比較高,采用的電子元器件大多都是中高端級別的,尤其是時鐘晶體振蕩器,應用的類型主要有XO晶振,VCXO晶振這兩種.那么XO和VCXO這兩大類晶振有什么區別,哪種更適合用于異步時鐘和同步時鐘呢?本文將仔細的解答和說明,二者之間的關系與區別,以及是如何使用到異步與同步時鐘系統的.

為特定應用選擇合適的器件取決于許多因素,包括時鐘是否必須與外部提供的參考時鐘同步,處理器的系統架構和高速串行數據傳輸IC,以及頻率和最終應用的抖動要求.在高性能應用中,低抖動和低相位噪聲至關重要,因為它們對高速串行數據傳輸應用中的誤碼率和模數轉換器的信噪比有直接影響.

隨著硬件設計人員在單一硬件設計中需要支持越來越多的標準,協議和規范,高性能應用中的硬件設計(如網絡,無線/RF傳輸,廣播視頻以及測試和測量)變得越來越復雜.一些例子說明了這種趨勢.最新的網絡設備不僅支持SONET/SDH和以太網,還支持高清視頻傳輸.下一代無線基礎設施設備旨在支持WiMAX和LTE(長期演進).廣播視頻設備涵蓋各種功能,包括圖像捕獲,編碼,解碼,處理和視頻傳輸,必須支持NTSC和PAL標準,以確保全球兼容性.隨著傳統上不同類型設備之間的界限變得越來越模糊,出現了單獨的挑戰.在這些應用中設計最有效的時序架構至關重要,以最大限度地縮短設計時間和BOM成本.

異步時鐘

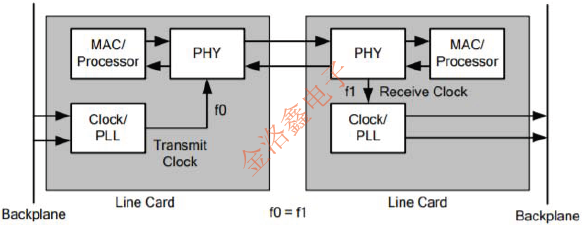

最簡單的時鐘生成源是OSC晶振(XO),它為單個組件生成單個輸出頻率.XO通常用于異步應用,如圖1所示.每個振蕩器提供本地參考以維護兩個獨立的時鐘域.系統操作要求XO頻率接近但不相同.該架構非常適合突發模式流量應用.連續通信需要比特或數據包填充和FIFO管理,以防止上溢/下溢情況.視頻處理設備和10/100/1000BaseT以太網是使用異步時鐘的應用程序的示例.XO選擇應基于最終應用的頻率,抖動和穩定性要求. 同步時鐘

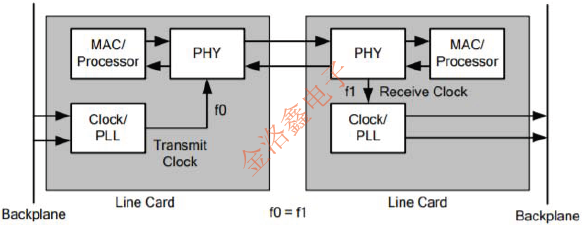

同步時鐘最常用于需要連續通信的應用程序中.必須最小化網絡延遲和延遲的可變性.為實現此目的,包括SONET/SDH,同步以太網(SyncE),無線回程和視頻傳輸在內的應用要求源和目標以相同的頻率運行.在發送側,為高速SerDes的發送路徑提供定時的時鐘被鎖定為高度精確的參考時鐘.主要和次要參考時鐘都是從集中定時源(例如GPS)提供的.PLL用于鎖定此背板參考,衰減時鐘信號上的抖動以消除不需要的噪聲,并為PHY提供低抖動輸出時鐘.在接收端,時鐘和數據恢復(CDR)單元用于恢復系統時鐘.

根據應用,該CDR可以是外部組件或集成在PHY內.Oscillator可用于使CDR居中以提供快速獲取和鎖定.恢復的時鐘通過另一個PLL,將時鐘頻率降低到較低的速率.本地定時可以與此時鐘同步,也可以與同步到集中定時源的另一個本地時鐘同步.與源的同步確保了網絡中所有節點的時鐘同步.根據系統要求,本應用中使用的PLL可能需要低環路帶寬來濾除時鐘信號中不需要的抖動.

圖2.同步時鐘示例

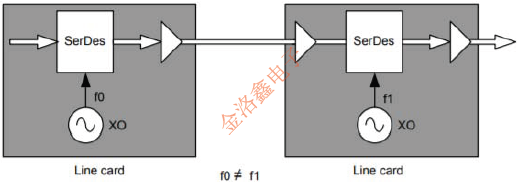

PLL可以使用集成時鐘IC或壓控晶體振蕩器(VCXO),相位檢測器和環路濾波器實現離散.當需要盡可能低的抖動和最佳可能的相位噪聲時,優選分立解決方案.在某些應用中,處理器或ASIC將相位檢測器和電荷泵集成在IC內,因此只需要VCXO壓控振蕩器和外部環路濾波器,如下面的圖3所示.

但是,離散PLL解決方案存在多種缺點.分立式PLL需要模擬設計專業知識,并且對板級噪聲敏感,因此在設計和PCB布局中必須特別小心.此外,分立PLL通常提供單個輸出頻率.如果設計的頻率要求發生變化,則必須提供單獨的VCXO.在某些應用中,需要多個壓控振蕩器來生成應用中的所有所需頻率,從而增加了BOM的復雜性.為了解決這些缺點,現在可以通過SiliconLab的Si571實現雙通道,四通道甚至任何速率的I2C可編程VCXO,通過用單個器件替換多個分立VCXO來滿足多速率應用.

另一種方法是使用抖動衰減時鐘倍頻器IC,它集成了片內PLL電路.時鐘倍頻器保持對參考時鐘的鎖定,濾除不需要的抖動,并為發送器生成倍頻輸出時鐘.在時鐘倍頻器IC選擇中必須特別小心,因為所有時鐘倍頻器都不相同.對于高速串行數據傳輸應用,只有最高性能的時鐘倍頻器IC才能提供滿足最終應用要求所需的抖動性能.

關鍵規范是最大抖動生成,而不是典型的抖動生成.指定最大抖動的時鐘倍頻器使硬件設計人員能夠在電路板中的數據路徑和定時組件之間分配抖動預算,并確保在所有條件下都有足夠的余量.另外,檢查時鐘倍頻器IC上可用的環路帶寬選項.如果需要參考時鐘的抖動衰減,則環路帶寬通常必須為1kHz或更低.最后,確認時鐘倍頻器IC支持所有必需的頻率規劃.Silicon晶振Si5319是一個提供抖動衰減和任意速率頻率合成的頻率捷變時鐘倍頻器的例子.

最后,當需要系統級時鐘功能時,時鐘解決方案優于離散解決方案.一個例子是輸入時鐘之間的無中斷切換,其中時鐘監視主參考時鐘的質量,并在檢測到主時鐘上的報警條件時切換到輔助參考.另一種流行的系統級時鐘要求是保持,其中時鐘在沒有有效參考時鐘的情況下繼續產生穩定的輸出時鐘.可以從多個供應商處獲得滿足這些系統級要求的時鐘.

為特定應用選擇合適的器件取決于許多因素,包括時鐘是否必須與外部提供的參考時鐘同步,處理器的系統架構和高速串行數據傳輸IC,以及頻率和最終應用的抖動要求.在高性能應用中,低抖動和低相位噪聲至關重要,因為它們對高速串行數據傳輸應用中的誤碼率和模數轉換器的信噪比有直接影響.

隨著硬件設計人員在單一硬件設計中需要支持越來越多的標準,協議和規范,高性能應用中的硬件設計(如網絡,無線/RF傳輸,廣播視頻以及測試和測量)變得越來越復雜.一些例子說明了這種趨勢.最新的網絡設備不僅支持SONET/SDH和以太網,還支持高清視頻傳輸.下一代無線基礎設施設備旨在支持WiMAX和LTE(長期演進).廣播視頻設備涵蓋各種功能,包括圖像捕獲,編碼,解碼,處理和視頻傳輸,必須支持NTSC和PAL標準,以確保全球兼容性.隨著傳統上不同類型設備之間的界限變得越來越模糊,出現了單獨的挑戰.在這些應用中設計最有效的時序架構至關重要,以最大限度地縮短設計時間和BOM成本.

異步時鐘

最簡單的時鐘生成源是OSC晶振(XO),它為單個組件生成單個輸出頻率.XO通常用于異步應用,如圖1所示.每個振蕩器提供本地參考以維護兩個獨立的時鐘域.系統操作要求XO頻率接近但不相同.該架構非常適合突發模式流量應用.連續通信需要比特或數據包填充和FIFO管理,以防止上溢/下溢情況.視頻處理設備和10/100/1000BaseT以太網是使用異步時鐘的應用程序的示例.XO選擇應基于最終應用的頻率,抖動和穩定性要求. 同步時鐘

同步時鐘最常用于需要連續通信的應用程序中.必須最小化網絡延遲和延遲的可變性.為實現此目的,包括SONET/SDH,同步以太網(SyncE),無線回程和視頻傳輸在內的應用要求源和目標以相同的頻率運行.在發送側,為高速SerDes的發送路徑提供定時的時鐘被鎖定為高度精確的參考時鐘.主要和次要參考時鐘都是從集中定時源(例如GPS)提供的.PLL用于鎖定此背板參考,衰減時鐘信號上的抖動以消除不需要的噪聲,并為PHY提供低抖動輸出時鐘.在接收端,時鐘和數據恢復(CDR)單元用于恢復系統時鐘.

根據應用,該CDR可以是外部組件或集成在PHY內.Oscillator可用于使CDR居中以提供快速獲取和鎖定.恢復的時鐘通過另一個PLL,將時鐘頻率降低到較低的速率.本地定時可以與此時鐘同步,也可以與同步到集中定時源的另一個本地時鐘同步.與源的同步確保了網絡中所有節點的時鐘同步.根據系統要求,本應用中使用的PLL可能需要低環路帶寬來濾除時鐘信號中不需要的抖動.

圖2.同步時鐘示例

另一種方法是使用抖動衰減時鐘倍頻器IC,它集成了片內PLL電路.時鐘倍頻器保持對參考時鐘的鎖定,濾除不需要的抖動,并為發送器生成倍頻輸出時鐘.在時鐘倍頻器IC選擇中必須特別小心,因為所有時鐘倍頻器都不相同.對于高速串行數據傳輸應用,只有最高性能的時鐘倍頻器IC才能提供滿足最終應用要求所需的抖動性能.

關鍵規范是最大抖動生成,而不是典型的抖動生成.指定最大抖動的時鐘倍頻器使硬件設計人員能夠在電路板中的數據路徑和定時組件之間分配抖動預算,并確保在所有條件下都有足夠的余量.另外,檢查時鐘倍頻器IC上可用的環路帶寬選項.如果需要參考時鐘的抖動衰減,則環路帶寬通常必須為1kHz或更低.最后,確認時鐘倍頻器IC支持所有必需的頻率規劃.Silicon晶振Si5319是一個提供抖動衰減和任意速率頻率合成的頻率捷變時鐘倍頻器的例子.

最后,當需要系統級時鐘功能時,時鐘解決方案優于離散解決方案.一個例子是輸入時鐘之間的無中斷切換,其中時鐘監視主參考時鐘的質量,并在檢測到主時鐘上的報警條件時切換到輔助參考.另一種流行的系統級時鐘要求是保持,其中時鐘在沒有有效參考時鐘的情況下繼續產生穩定的輸出時鐘.可以從多個供應商處獲得滿足這些系統級要求的時鐘.

下表總結了何時應使用XO,VCXO或時鐘解決方案.

| XO | VCXO | 時鐘 | |

| 主要功能 |

異步定時 CDR參考時鐘 |

同步定時 時鐘倍增/抖動衰減作為離散鎖相環的一部分 生成單輸出時鐘 |

同步定時 時鐘倍增 抖動衰減 生成多路輸出時鐘 系統級功能(保持、無中斷切換) |

| 頻率 | 固定 | 調諧范圍內的連續變化(典型值+/-100ppm) | 可通過?Pinterface重新配置以支持大量非頻率計劃 |

| 設計復雜性 | 低 | 高 | 低 |

| 綜合 | 高 | 低 | 高 |

| 抖動濾波器 | 沒有 | 是(離散) | 是(綜合) |

| 使用時間 | 需要本地振蕩器 |

要求最低的相位噪聲/抖動性能 集成在碳化硅/FPGA中的鎖相環電路 |

集成解決方案是首選 需要抖動衰減和/或時鐘倍增 需要頻率靈活性 需要系統級功能 |

表1定時解決方案指南

遵循上面列出的準則,為即將到來的設計選擇合適的時鐘或振蕩器可以大大簡化.硅實驗室提供各種抖動衰減時鐘乘法器、時鐘發生器、時鐘緩沖器、XO和壓控晶振,以滿足客戶獨特的時序要求.

正在載入評論數據...

發表評論:

| 姓名: | |

| 郵箱: | |

| 正文: | |

歡迎參與討論,請在這里發表您的看法、交流您的觀點。

相關資訊

- [2024-03-08]IQD晶體尺寸縮小的設計效果LFXT...

- [2024-03-07]Golledge衛星通信中的頻率控制產...

- [2024-03-07]Golledge工業自動化和控制系統中...

- [2024-03-06]MTI-milliren恒溫晶振222系列振...

- [2024-03-06]MTI-milliren低G靈敏度銫原子鐘...

- [2024-03-05]GEYER高穩定性KXO-V93T低功耗32...

- [2024-03-02]NEL為系統關鍵應用程序設計和制...

- [2024-01-06]溫補補償振蕩器的原理及特點

業務經理

業務經理 客服經理

客服經理