當晶振遇到PCB線路板而產生的故事

來源:http://m.11ed.cn 作者:jinluodz 2013年07月12

時不時會接到客戶抱怨晶振與PCB布線不吻合,或晶振安裝于板內后,而引起的不良或損壞。了解于此,我司研發技術部門根據此類問題,而得出的結論。

晶振和芯片的距離一般要盡量靠近,一般指的是無源晶振,那么有源晶振布線有什么要求嗎?有源晶振能驅動多少個芯片呢?

有源晶振也不能輸出接長線。

時鐘源通常是系統中最嚴重的EMI輻射源,如果接長線,其結果是長線就成了天線,這在很多應用中是不準許的,所有時鐘源都必須盡量靠近相關器件,必要時用多個時鐘源,不得以下可以采用多層PCB將時鐘連線屏蔽。有源晶振的輸出一般是標準TTL規格,至于能驅動多少芯片要看這些芯片的特性。

時鐘布哪一層?

夾心層,其上下都是覆地

但這種方法只有在不得以下為之,而且成本未必低于多時鐘(多層PCB的價格明顯高于雙面板),要過某些強制標準的產品盡量不要這么干。

1. Crystal下不可走線,電路儘量靠近chip端。

2. trace盡量短,與其他信號需20mil間距,最好使用ground trace與其他信號隔離.

3.Crystal底下盡量不要走線,如果實在要走線的話, 不能走線進Crystal pin腳周圍50mil之內. 尤其避免高速訊號。.

晶振信號線盡可能短,需要包地(因為有噪聲,本質就是怕它影響到別人,或者怕別人影響到他)。盡可能不穿孔,以為一個過孔會有0.5pF的寄生電容,另外,走線粗細要一致。

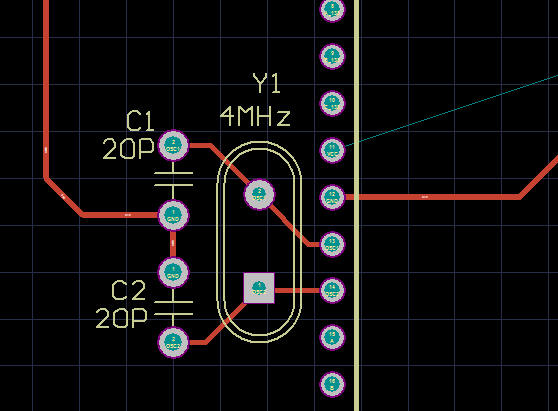

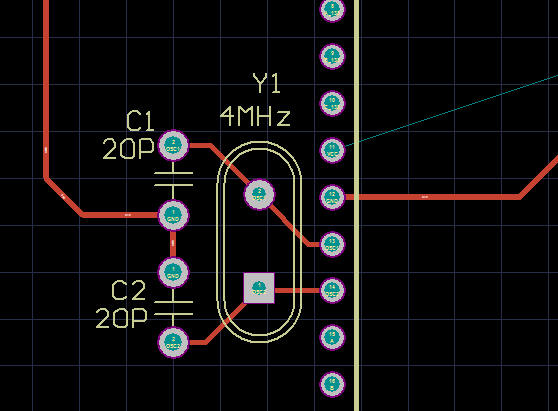

作個最簡單的例子,如以下插件石英晶振49/S的布線圖。

晶振和芯片的距離一般要盡量靠近,一般指的是無源晶振,那么有源晶振布線有什么要求嗎?有源晶振能驅動多少個芯片呢?

有源晶振也不能輸出接長線。

時鐘源通常是系統中最嚴重的EMI輻射源,如果接長線,其結果是長線就成了天線,這在很多應用中是不準許的,所有時鐘源都必須盡量靠近相關器件,必要時用多個時鐘源,不得以下可以采用多層PCB將時鐘連線屏蔽。有源晶振的輸出一般是標準TTL規格,至于能驅動多少芯片要看這些芯片的特性。

時鐘布哪一層?

夾心層,其上下都是覆地

但這種方法只有在不得以下為之,而且成本未必低于多時鐘(多層PCB的價格明顯高于雙面板),要過某些強制標準的產品盡量不要這么干。

1. Crystal下不可走線,電路儘量靠近chip端。

2. trace盡量短,與其他信號需20mil間距,最好使用ground trace與其他信號隔離.

3.Crystal底下盡量不要走線,如果實在要走線的話, 不能走線進Crystal pin腳周圍50mil之內. 尤其避免高速訊號。.

晶振信號線盡可能短,需要包地(因為有噪聲,本質就是怕它影響到別人,或者怕別人影響到他)。盡可能不穿孔,以為一個過孔會有0.5pF的寄生電容,另外,走線粗細要一致。

作個最簡單的例子,如以下插件石英晶振49/S的布線圖。

正在載入評論數據...

相關資訊

- [2024-03-08]IQD晶體尺寸縮小的設計效果LFXT...

- [2024-03-07]Golledge衛星通信中的頻率控制產...

- [2024-03-07]Golledge工業自動化和控制系統中...

- [2024-03-06]MTI-milliren恒溫晶振222系列振...

- [2024-03-06]MTI-milliren低G靈敏度銫原子鐘...

- [2024-03-05]GEYER高穩定性KXO-V93T低功耗32...

- [2024-03-02]NEL為系統關鍵應用程序設計和制...

- [2024-01-06]溫補補償振蕩器的原理及特點

業務經理

業務經理 客服經理

客服經理